# **8051 Microcontroller Family Compatible**

## 256K

# X88257

# 32,768 x 8 Bit

# E<sup>2</sup> Micro-Peripheral

#### FEATURES

- Multiplexed Address/Data Bus —Direct Interface to Popular 8051 Family

- High Performance CMOS —Fast Access Time, 120ns

- -Fast Access Time, 120 -Low Power

- -LOW FOWEI 60mA Active Maxir

- ---60mA Active Maximum ---500µA Standby Maximum

- Software Data Protection

- Toggle Bit Polling

- -Early End of Write Detection

- Page Mode Write

Allows up to 128 Bytes to be Written in

One Write Cycle

- High Reliability

—Endurance: 10,000 Write Cycle

—Data Retention: 100 Years

- 28-Lead PDIP Package

- 28-Lead SOIC Package

- 32-Lead PLCC Package

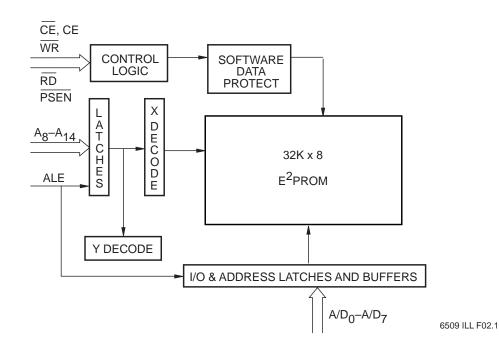

**FUNCTIONAL DIAGRAM**

### DESCRIPTION

The X88257 is an 32K x 8 E<sup>2</sup>PROM fabricated with advanced CMOS Textured Poly Floating Gate Technology. The X88257 features a multiplexed address and data bus allowing direct interface to a variety of popular single-chip microcontrollers operating in expanded multiplexed mode without the need for additional interface circuitry.

#### **PIN DESCRIPTIONS**

#### Address/Data (A/D<sub>0</sub>-A/D<sub>7</sub>)

Multiplexed low-order addresses and data. The addresses flow into the device while ALE is HIGH. After ALE transitions from a HIGH to LOW the addresses are latched. Once the addresses are latched these pins input data or output data depending on  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ ,  $\overline{\text{PSEN}}$ , and  $\overline{\text{CE}}$ .

#### Addresses (A<sub>8</sub>-A<sub>14</sub>)

High order addresses flow into the device when ALE =  $V_{\text{IH}}$  and are latched when ALE goes LOW.

#### Chip Enable (CE)

The Chip Enable input must be LOW to enable all read/ write operations. When  $\overline{CE}$  is HIGH, ALE is LOW, and CE is LOW, the X88257 is placed in the low power standby mode. If  $\overline{CE}$  is used to select the device, the CE must be tied LOW.

#### Chip Enable (CE)

Chip enable is active HIGH. When CE is used to select the device, the  $\overline{\text{CE}}$  must be tied HIGH.

#### Program Store Enable (PSEN)

When the X88257 is to be used in a 8051-based system,  $\overrightarrow{\text{PSEN}}$  is tied directly to the microcontroller's  $\overrightarrow{\text{PSEN}}$  output.

#### Read (RD)

When the X88257 is to be used in a 8051-based system,  $\overline{\text{RD}}$  is tied directly to the microcontroller's  $\overline{\text{RD}}$  output.

#### Write (WR)

When the X88257 is to be used in a 8051-based system,  $\overline{WR}$  is tied directly to the microcontroller's  $\overline{WR}$  output.

#### Address Latch Enable (ALE)

Addresses flow through the latches to address decoders when ALE is HIGH and are latched when ALE transitions from a HIGH to LOW.

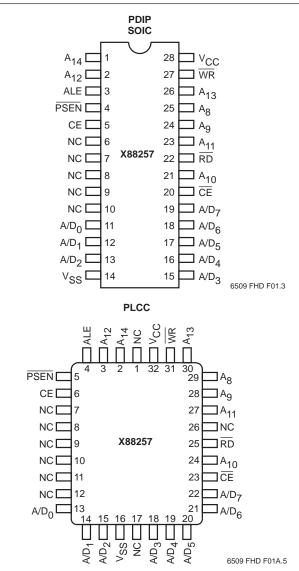

#### **PIN CONFIGURATION**

#### **PIN NAMES**

| Symbol                             | Description                |

|------------------------------------|----------------------------|

| ALE                                | Address Latch Enable       |

| A/D <sub>0</sub> -A/D <sub>7</sub> | Address Inputs/Data I/O    |

| A8-A14                             | Address Inputs             |

| RD                                 | Read Input                 |

| WR                                 | Write Input                |

| PSEN                               | Program Store Enable Input |

| CE, CE                             | Chip Enable                |

| V <sub>SS</sub>                    | Ground                     |

| Vcc                                | Supply Voltage             |

| NC                                 | No Connect                 |

|                                    | 6500 DOM T01 1             |

6509 PGM T01.1

# X88257

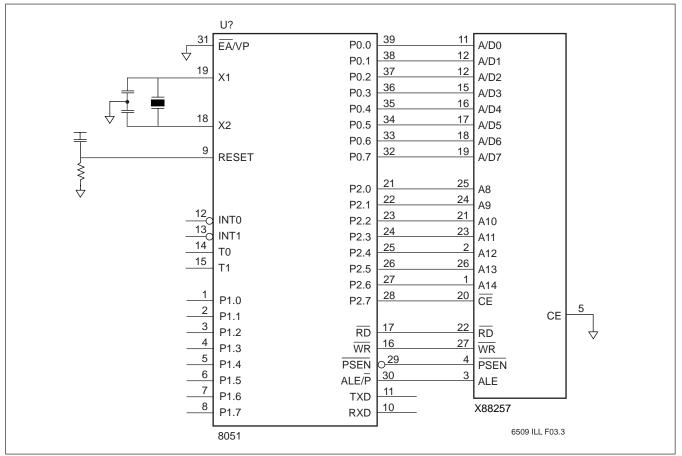

#### **TYPICAL APPLICATION**

#### PRINCIPLES OF OPERATION

The X88257 is a highly integrated peripheral device for a wide variety of single-chip microcontrollers. The X88257 provides 32K-bytes of 5V E<sup>2</sup>PROM which can be used either for program storage, data storage or a combination of both, in systems based upon Harvard (80XX) architectures. The X88257 incorporates the interface circuitry normally needed to decode the control signals and demultiplex the address/data bus to provide a "seamless" interface.

The interface inputs on the X88257 are configured such that it is possible to directly connect them to the proper interface signals of the appropriate single-chip microcontroller. In the Harvard type system, the reading of data from the chip is controlled either by the PSEN or the RD signal, which essentially maps the X88257 into both the Program and the Data Memory address map.

The X88257 also features the industry standard 5V E<sup>2</sup>PROM characteristics such as byte or page mode write and Toggle Bit Polling.

#### **DEVICE OPERATION**

#### Modes—Mixed Program/Data Memory

By properly assigning the address spaces, a single X88257 can be used as both the program and data memory. This would be accomplished by connecting all the 8051 control outputs to the corresponding inputs of the X88257.

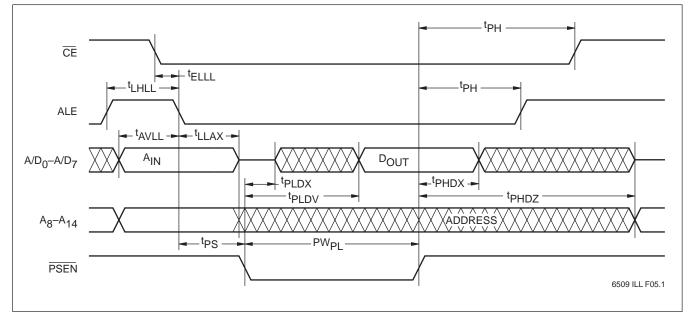

#### **Program Memory Mode**

This mode of operation is read-only. The  $\overrightarrow{PSEN}$  and  $\overrightarrow{ALE}$  inputs of the X88257 are tied directly to the  $\overrightarrow{PSEN}$  and  $\overrightarrow{ALE}$  outputs of the microcontroller. The  $\overrightarrow{RD}$  and  $\overrightarrow{WR}$  inputs are tied HIGH.

When ALE is HIGH, the A/D<sub>0</sub>–A/D<sub>7</sub> and A<sub>8</sub>–A<sub>14</sub> addresses flow into the device. The addresses, both lowand high-order, are latched when ALE transitions LOW (V<sub>IL</sub>). PSEN will then go LOW and after t<sub>PLDV</sub>; Valid data is presented on the A/D<sub>0</sub>–A/D<sub>7</sub> pins.  $\overline{CE}$  must be LOW during the entire operation.

## X88257

#### DATA MEMORY MODE

**MODE SELECTION**

This mode of operation allows both read and write functions. The  $\overline{\text{PSEN}}$  input is tied to  $V_{IH}$  or to  $V_{CC}$  through a pull-up resistor. The ALE,  $\overline{\text{RD}}$ , and  $\overline{\text{WR}}$  inputs are tied directly to the microcontroller ALE,  $\overline{\text{RD}}$ , and  $\overline{\text{WR}}$  outputs.

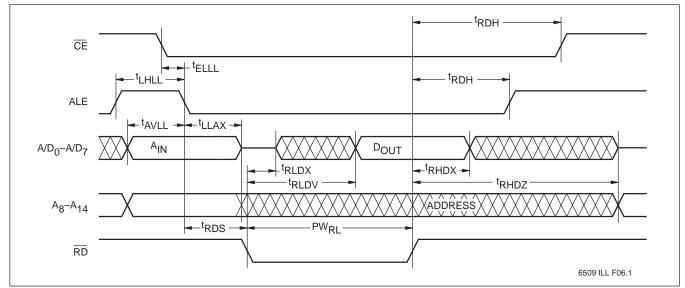

#### Read

This operation is quite similar to the program memory read. A HIGH to LOW transition on ALE latches the

addresses and the data will be output on the AD pins after  $\overline{\text{RD}}$  goes LOW (t<sub>RLDV</sub>).

#### Write

A write is performed by latching the addresses on the falling edge of ALE. Then  $\overline{WR}$  is strobed LOW followed by valid data being presented at the A/D<sub>0</sub>–A/D<sub>7</sub> pins. The data will be latched into the X88257 on the rising edge of  $\overline{WR}$ . To write to the X88257, a three-byte command sequence must precede the byte(s) being written. (See Software Data Protection.)

| CE   | PSEN | RD   | WR   | Mode                  | I/O    | Power          |

|------|------|------|------|-----------------------|--------|----------------|

| Vcc  | Х    | Х    | Х    | Standby               | High Z | Standby (CMOS) |

| HIGH | Х    | Х    | Х    | Standby               | High Z | Standby (TTL)  |

| LOW  | LOW  | HIGH | HIGH | Read D <sub>OUT</sub> |        | Active         |

| LOW  | HIGH | LOW  | HIGH | Read                  | Dout   | Active         |

| LOW  | HIGH | HIGH |      | Write                 | DIN    | Active         |

6509 PGM T02

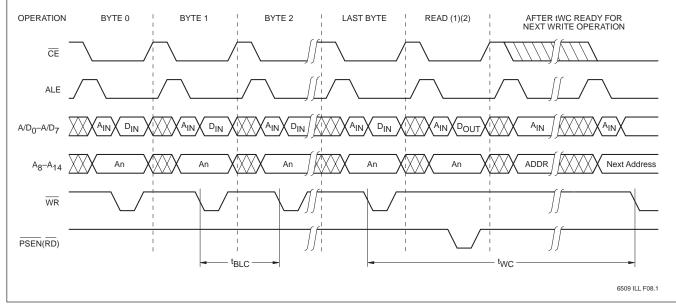

#### PAGE WRITE OPERATION

Regardless of the microcontroller employed, the X88257 supports page mode write operations. This allows the microcontroller to write from 1 to 128 bytes of data to the X88257. Each individual write within a page write operation must conform to the byte write timing requirements.

The falling edge of  $\overline{\text{WR}}$  starts a timer delaying the internal programming cycle 100µs. Therefore, each successive write operation must begin within 100µs of the last byte written. The following waveforms illustrate the sequence and timing requirements.

Notes: (1) For each successive write within a page write cycle  $A_7-A_{14}$  must be the same.

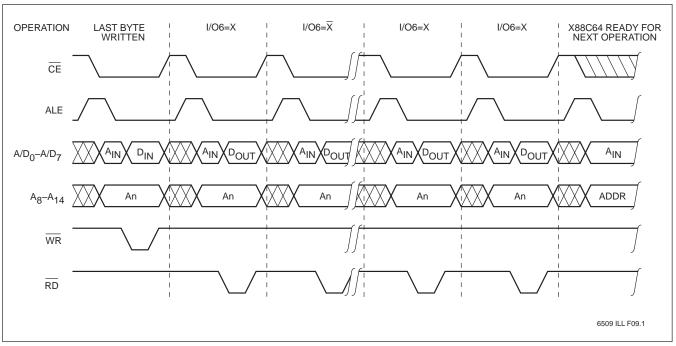

#### TOGGLE BIT POLLING

Because the typical write timing is less than the specified 5ms, Toggle Bit Polling has been provided to determine the early end of write. During the internal programming cycle  $I/O_6$  will toggle from "1" to "0" and "0" to "1" on

subsequent attempts to read the device. When the internal cycle is complete the toggling will cease and the device will be accessible for additional read or write operations.

#### Toggle Bit Polling RD/WR Control

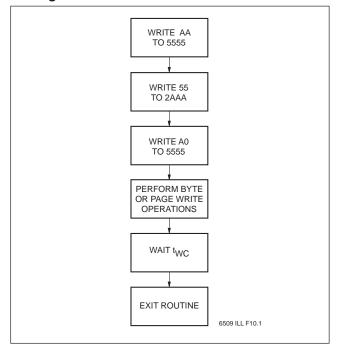

#### SOFTWARE DATA PROTECTION

Software Data Protection (SDP) is employed to protect the entire array against inadvertent writes. To write to the X88257, a three-byte command sequence must precede the byte(s) being written. All write operations, both the command sequence and any data write operations must conform to the page write timing requirements.

#### Writing with SDP

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature under Bias     | . –65°C to +135°C |

|----------------------------|-------------------|

| Storage Temperature        | . –65°C to +150°C |

| Voltage on any Pin with    |                   |

| Respect to V <sub>SS</sub> | –1V to +7V        |

| D.C. Output Current        | 5mA               |

| Lead Temperature           |                   |

| (Soldering, 10 seconds)    | 300°C             |

#### **\*COMMENT**

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

| Temperature | Min.  | Max.           |

|-------------|-------|----------------|

| Commercial  | 0°C   | +70°C          |

| Industrial  | _40°C | +85°C          |

| Military    | –55°C | +125°C         |

|             |       | 6509 PGM T03.1 |

| Supply Voltage | Limits         |

|----------------|----------------|

| X88257         | 5V ±10%        |

|                | 6509 PGM T04.1 |

### D.C. OPERATING CHARACTERISTICS (Over recommended operating conditions unless otherwise specified.)

|                       |                                   | Lir  | nits                  |       |                                                                                                                    |

|-----------------------|-----------------------------------|------|-----------------------|-------|--------------------------------------------------------------------------------------------------------------------|

| Symbol                | Parameter                         | Min. | Max.                  | Units | Test Conditions                                                                                                    |

| Icc                   | V <sub>CC</sub> Current (Active)  |      | 60                    | mA    | $\overline{CE} = \overline{RD} = V_{IL}$ , All I/O's =<br>Open,Other Inputs = V <sub>CC</sub>                      |

| ISB1(CMOS)            | V <sub>CC</sub> Current (Standby) |      | 500                   | μΑ    | $\overline{CE} = V_{CC} - 0.3V$ , All I/O's =<br>Open,Other Inputs = V <sub>CC</sub> - 0.3V, ALE = V <sub>IL</sub> |

| I <sub>SB2(TTL)</sub> | V <sub>CC</sub> Current (Standby) |      | 6                     | mA    | $\overline{CE} = V_{IH}$ , All I/O's = Open, Other<br>Inputs = V <sub>IH</sub> , ALE = V <sub>IL</sub>             |

| ILI                   | Input Leakage Current             |      | 10                    | μΑ    | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                                      |

| Ilo                   | Output Leakage Current            |      | 10                    | μΑ    | $V_{OUT} = V_{SS}$ to $V_{CC}$ ,<br>$\overline{RD} = V_{IH} = \overline{PSEN}$                                     |

| V <sub>IL</sub> (3)   | Input LOW Voltage                 | -1   | 0.8                   | V     |                                                                                                                    |

| V <sub>IH</sub> (3)   | Input HIGH Voltage                | 2    | V <sub>CC</sub> + 0.5 | V     |                                                                                                                    |

| Vol                   | Output LOW Voltage                |      | 0.4                   | V     | I <sub>OL</sub> = 2.1mA                                                                                            |

| Voн                   | Output HIGH Voltage               | 2.4  |                       | V     | І <sub>ОН</sub> = -400μА                                                                                           |

|                       |                                   |      | 1                     |       | 6509 PGM T05                                                                                                       |

#### **CAPACITANCE** $T_A = +25^{\circ}C$ , f = 1MHz, $V_{CC} = 5V$

| Symbol              | Test                     | Max. | Units | Conditions     |

|---------------------|--------------------------|------|-------|----------------|

| CI/O <sup>(4)</sup> | Input/Output Capacitance | 10   | pF    | $V_{I/O} = 0V$ |

| C <sub>IN</sub> (4) | Input Capacitance        | 6    | pF    | $V_{IN} = 0V$  |

|                     |                          |      |       | 6509 PGM T0    |

#### **POWER-UP TIMING**

| Symbol               | Parameter         | Max. | Units |

|----------------------|-------------------|------|-------|

| tpur <sup>(4)</sup>  | Power-Up to Read  | 1    | ms    |

| t <sub>PUW</sub> (4) | Power-Up to Write | 5    | ms    |

|                      |                   |      |       |

6509 PGM T07

Notes: (3)  $V_{IL}$  min. and  $V_{IH}$  max. are for reference only and are not tested. (4) This parameter is periodically sampled and not 100% tested.

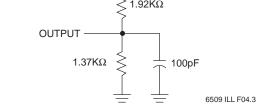

#### A.C. CONDITIONS OF TEST

| Input Pulse Levels | 0V to 3V |

|--------------------|----------|

| Input Rise and     |          |

| Fall Times         | 10ns     |

| Input and Output   |          |

| Timing Levels      | 1.5V     |

|                    |          |

6509 PGM T08.1

# 5V 1.92KΩ

**EQUIVALENT A.C. TEST CIRCUIT**

#### A.C. CHARACTERISTICS (Over the recommended operating conditions unless otherwise specified.)

|                                  | Min.                                                                                                                                                                                                                                                                                                                   | Max.                                                                                                                                                                                    | Units                                                                                                                                                                                                       |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE Pulse Width                  | 80                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                         | ns                                                                                                                                                                                                          |

| Address Setup Time               | 20                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                         | ns                                                                                                                                                                                                          |

| Address Hold Time                | 30                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                         | ns                                                                                                                                                                                                          |

| PSEN Read Access Time            |                                                                                                                                                                                                                                                                                                                        | 120                                                                                                                                                                                     | ns                                                                                                                                                                                                          |

| Data Hold Time                   | 0                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                         | ns                                                                                                                                                                                                          |

| Chip Enable Setup Time           | 7                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                         | ns                                                                                                                                                                                                          |

| PSEN Pulse Width                 | 150                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                         | ns                                                                                                                                                                                                          |

| PSEN Setup Time                  | 30                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                         | ns                                                                                                                                                                                                          |

| PSEN Hold Time                   | 20                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                         | ns                                                                                                                                                                                                          |

| PSEN Disable to Output in High Z |                                                                                                                                                                                                                                                                                                                        | 50                                                                                                                                                                                      | ns                                                                                                                                                                                                          |

| PSEN to Output in Low Z          | 10                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                         | ns                                                                                                                                                                                                          |

|                                  | Address Setup Time         Address Hold Time         PSEN Read Access Time         Data Hold Time         Chip Enable Setup Time         PSEN Pulse Width         PSEN Setup Time         PSEN Hold Time         PSEN Hold Time         PSEN Hold Time         PSEN Hold Time         PSEN Disable to Output in High Z | Address Setup Time20Address Hold Time30PSEN Read Access Time0Data Hold Time0Chip Enable Setup Time7PSEN Pulse Width150PSEN Setup Time30PSEN Hold Time20PSEN Disable to Output in High Z | Address Setup Time20Address Hold Time30PSEN Read Access Time120Data Hold Time0Chip Enable Setup Time7PSEN Pulse Width150PSEN Setup Time30PSEN Hold Time20PSEN Hold Time20PSEN Disable to Output in High Z50 |

#### **PSEN Controlled Read Cycle**

#### **PSEN Controlled Read Timing Diagram**

Note: (5) This parameter is periodically sampled and not 100% tested.

### **RD** Controlled Read Cycle

| Symbol                | Parameter                      | Min. | Max. | Units |

|-----------------------|--------------------------------|------|------|-------|

| tLHLL                 | ALE Pulse Width                | 80   |      | ns    |

| tavll                 | Address Setup Time             | 20   |      | ns    |

| tLLAX                 | Address Hold Time              | 30   |      | ns    |

| t <sub>RLDV</sub>     | RD Read Access Time            |      | 120  | ns    |

| trhdx                 | Data Hold Time                 | 0    |      | ns    |

| tELLL                 | Chip Enable Setup Time         | 7    |      | ns    |

| PW <sub>RL</sub>      | RD Pulse Width                 | 150  |      | ns    |

| tRDS                  | RD Setup Time                  | 30   |      | ns    |

| t <sub>RDH</sub>      | RD Hold Time                   | 20   |      | ns    |

| t <sub>RHDZ</sub> (6) | RD Disable to Output in High Z |      | 50   | ns    |

| t <sub>RLDX</sub> (6) | RD to Output in Low Z          | 0    |      | ns    |

| trldx (6)             | RD to Output in Low Z          | 0    |      |       |

### **RD** Controlled Read Timing Diagram

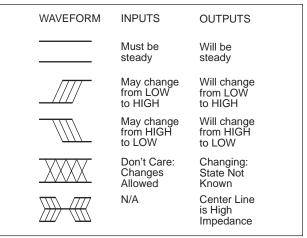

#### SYMBOL TABLE

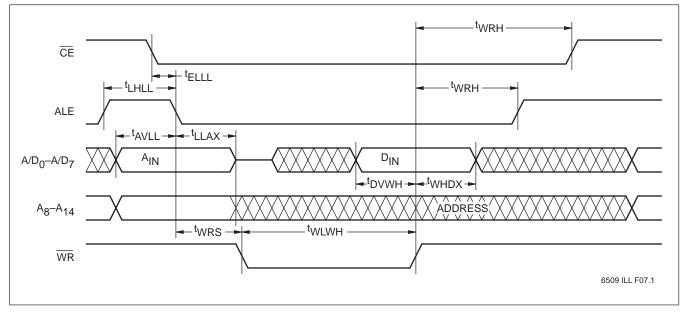

### WR Controlled Write Cycle

| Symbol                                   | Parameter                   | Min. | Max. | Units   |

|------------------------------------------|-----------------------------|------|------|---------|

| t <sub>LHLL</sub>                        | ALE Pulse Width             | 80   |      | ns      |

| tavll                                    | Address Setup Time          | 20   |      | ns      |

| t <sub>LLAX</sub>                        | Address Hold Time           | 30   |      | ns      |

| tDVWH                                    | Data Setup Time             | 50   |      | ns      |

| twhdx                                    | Data Hold Time              | 30   |      | ns      |

| tELLL                                    | Chip Enable Setup Time      | 7    |      | ns      |

| twLwH                                    | WR Pulse Width              | 120  |      | ns      |

| twrs                                     | WR Setup Time               | 30   |      | ns      |

| twrh                                     | WR Hold Time                | 20   |      | ns      |

| tBLC                                     | Byte Load Time (Page Write) | 0.5  | 100  | μs      |

| twc (7)                                  | Write Cycle Time            |      | 5    | ms      |

| L. L |                             | •    |      | 6509 PC |

### WR Controlled Write Timing Diagram

Note: (7) t<sub>WC</sub> is the minimum cycle time to be allowed from the system perspective unless polling techniques are used. It is the maximum time the device requires to automatically complete the internal write operation.

NOTES

NOTES

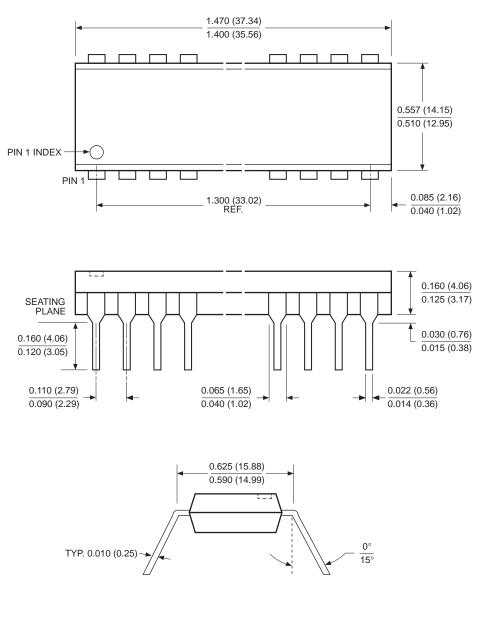

#### PACKAGING INFORMATION

28-LEAD PLASTIC DUAL IN-LINE PACKAGE TYPE P

NOTE: 1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS) 2. PACKAGE DIMENSIONS EXCLUDE MOLDING FLASH

3926 FHD F04

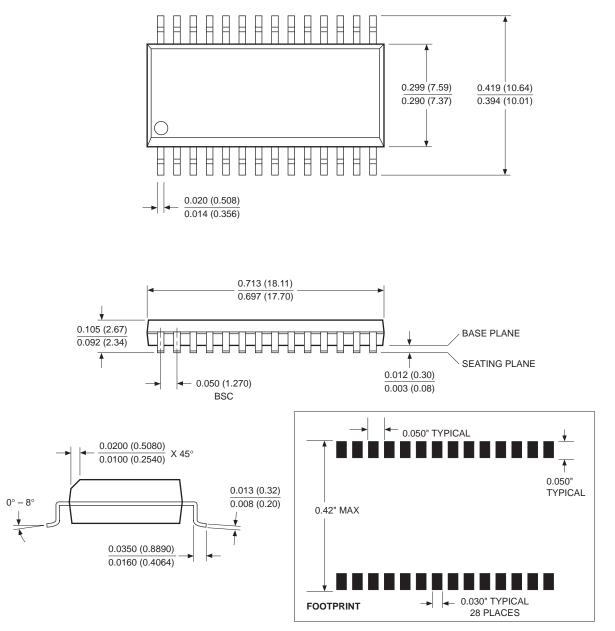

### PACKAGING INFORMATION

28-LEAD PLASTIC SMALL OUTLINE GULL WING PACKAGE TYPE S

NOTES:

1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

2. FORMED LEAD SHALL BE PLANAR WITH RESPECT TO ONE ANOTHER WITHIN 0.004 INCHES

3926 FHD F17

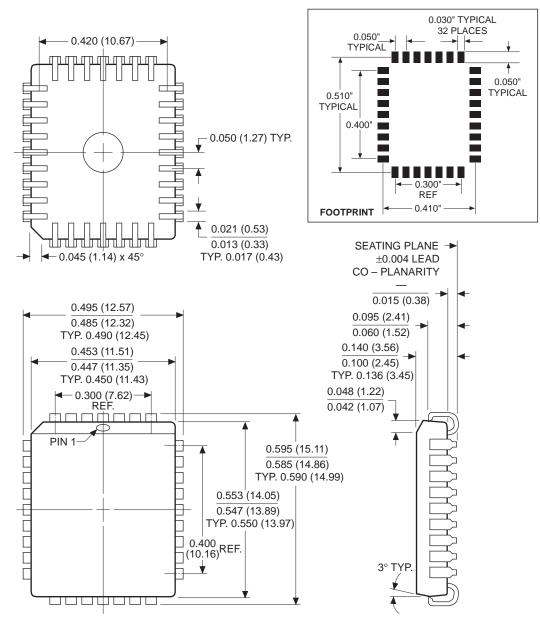

#### PACKAGING INFORMATION

32-LEAD PLASTIC LEADED CHIP CARRIER PACKAGE TYPE J

NOTES: 1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS) 2. DIMENSIONS WITH NO TOLERANCE FOR REFERENCE ONLY

3926 FHD F13

## X88257

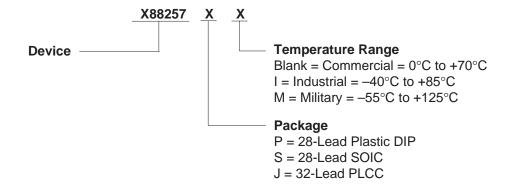

#### **ORDERING INFORMATION**

#### LIMITED WARRANTY

Devices sold by Xicor, Inc. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Xicor, Inc. makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Xicor, Inc. makes no warranty of merchantability or fitness tor any purpose. Xicor, Inc. reserves the right to discontinue production and change specifications and prices at any time and without notice.

Xicor, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Xicor, Inc. product. No other circuits, patents, licenses are implied.

#### **US. PATENTS**

Xicor products are covered by one or more of the following U.S. Patents: 4,263,664; 4,274,012; 4,300,212; 4,314,265; 4,326,134; 4,393,481; 4,404,475; 4,450,402; 4,486,769; 4,488,060; 4,520,461; 4,533,846; 4,599,706; 4,617,652; 4,668,932; 4,752,912; 4,829,482; 4,874,967; 4,883,976; 4,980,859; 5,012,132; 5,003,197; 5,023,694. Foreign patents and additional patents pending.

#### LIFE RELATED POLICY

In situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurrence.

Xicor's products are not authorized for use as critical components in life support devices or systems.

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its satety or effectiveness.